#### Università degli Studi di Pisa Dipartimento di Matematica Corso di Laurea Magistrale in Matematica

# Algebraic Techniques for Circuit Verification

Tesi di Laurea Magistrale

17 ottobre 2014

Candidato

Oscar Papini

Relatori Prof.ssa **Patrizia Gianni** Dott. **Barry Trager**

Anno Accademico 2013/2014

## **Contents**

| In | trodu | ıction  |                                                      | xi |

|----|-------|---------|------------------------------------------------------|----|

| 1  | Ree   | d-Solo: | mon Encoding and Decoding                            | 1  |

|    | 1.1   | How     | to Encode a Word                                     | 1  |

|    | 1.2   | How     | to Decode a Word                                     | 3  |

|    | 1.3   | The C   | Combined RS Encoder/Syndrome Generator               | 5  |

| 2  | The   | Comn    | nutative Algebra Approach                            | 9  |

|    | 2.1   | The N   | Nullstellensatz for Finite Fields                    | 9  |

|    | 2.2   | Verifi  | cation of Combinational Circuits                     | 11 |

|    | 2.3   | Deali   | ng with Time: the Polynomial Method                  | 14 |

|    | 2.4   | Deali   | ng with Time: the Module Method                      | 16 |

|    | 2.5   | A Firs  | st Result: Arbitrariness of the Coefficient Field    | 19 |

| 3  | The   | Differ  | rence Equations Approach                             | 21 |

|    | 3.1   | Differ  | rence Equations                                      | 21 |

|    | 3.2   | The Z   | Z-Transform                                          | 23 |

|    | 3.3   | Trans   | fer Functions                                        | 25 |

|    | 3.4   | Circu   | it Equivalence                                       | 26 |

| 4  | Cor   | rectnes | s of the Combined RS Encoder/Syndrome Generator      | 27 |

|    | 4.1   | Partic  | rular Instances of the Circuit                       | 27 |

|    |       | 4.1.1   | 2-Error-Correcting RS over $\mathbb{F}_8$            | 27 |

|    |       | 4.1.2   | 2-Error-Correcting RS over $\mathbb{F}_8$ with a Bug | 31 |

|    |       | 4.1.3   | 4-Error-Correcting RS over $\mathbb{F}_{32}$         | 32 |

|    | 4.2   | Gener   | ral Case                                             | 35 |

|    |       | 4.2.1   | Applying the Z-Transform                             | 37 |

|    |       | 4.2.2   | Equivalence to the Standard Encoder                  | 39 |

| Co | nclu  | sions a | and Further Developments                             | 47 |

| •   |          |

|-----|----------|

| 1V  | Contents |

| 1 V | Contents |

| A   | Erro  | r-Correcting Codes                      | 49 |

|-----|-------|-----------------------------------------|----|

|     | A.1   | Generality of Error-Correcting Codes    | 49 |

|     | A.2   | Some Examples of Error-Correcting Codes | 50 |

|     |       | A.2.1 Linear Codes                      | 50 |

|     |       | A.2.2 Cyclic Codes                      | 51 |

|     |       | A.2.3 BCH Codes                         | 52 |

|     | A.3   | Reed-Solomon Codes                      | 54 |

| В   | Logi  | c Circuits                              | 57 |

|     | B.1   | Combinational Circuits                  | 57 |

|     | B.2   | Sequential Circuits                     | 58 |

| Bil | bliog | raphy                                   | 59 |

# **List of Figures**

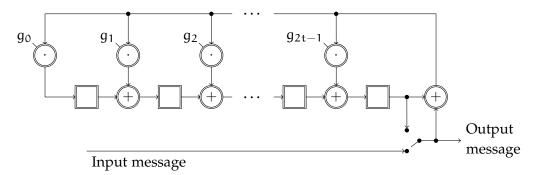

| 1.1 | A standard RS encoder                                             | 3  |

|-----|-------------------------------------------------------------------|----|

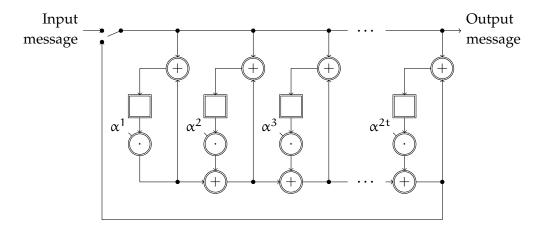

| 1.2 | Computation of the syndrome                                       | 4  |

| 1.3 | A set of circuit units for syndrome computation                   | 4  |

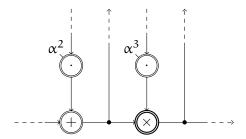

| 1.4 | The modified RS encoder with a linear feedback loop               | 5  |

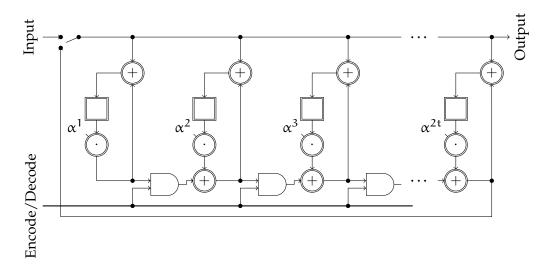

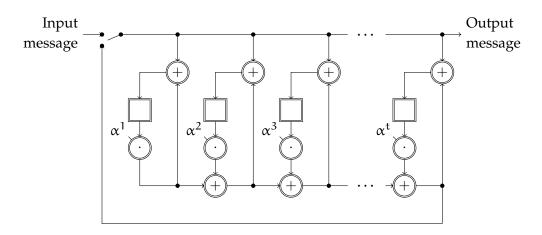

| 1.5 | The final version of the RS encoder                               | 6  |

| 1.6 | The combined encoder/syndrome generator                           | 6  |

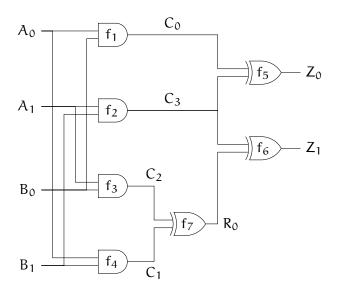

| 2.1 | A two-bit multiplier over $\mathbb{F}_4$                          | 12 |

| 2.2 | A recursive multiplier over $\mathbb{F}_q$                        | 15 |

| 2.3 | A recursive adder over $\mathbb{F}_q$                             | 18 |

| 3.1 | The same of Figure 1.2                                            | 25 |

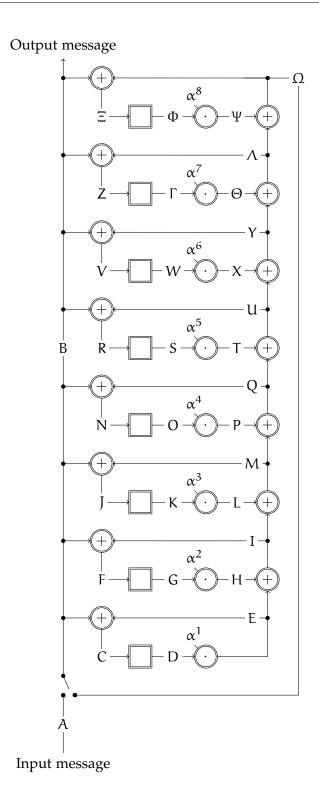

| 4.1 | The encoder of Figure 1.5 with $t = 2$                            | 28 |

| 4.2 | A bug in the circuit of Figure 4.1                                | 32 |

| 4.3 | The encoder with $t = 4$                                          | 33 |

| 4.4 | The same of Figure 1.5                                            | 36 |

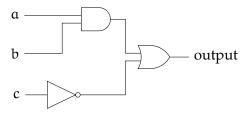

| B.1 | A combinational circuit that computes $(a \land b) \lor (\neg c)$ | 58 |

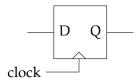

| B.2 | A typical memory register                                         | 58 |

vi List of Figures

# **List of Tables**

| 2.1 | Translation between Boolean expression and ring operation in a  |    |  |

|-----|-----------------------------------------------------------------|----|--|

|     | Boolean algebra                                                 | 12 |  |

| 2.2 | Polynomial translation of the gates of Figure 2.1               | 13 |  |

| 3.1 | Some common sequences with their Z-transforms                   | 24 |  |

| 4.1 | List of the polynomials associated to the circuit in Figure 4.1 | 29 |  |

viii List of Tables

# **List of Symbols**

### **Spaces and Algebraic Structures**

| $\frac{\mathbb{K}}{\mathbb{K}}$ , $\mathbb{F}_{\mathfrak{q}}$ | Field, finite field with q elements                                                                  |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| $\overline{\mathbb{K}}$                                       | Algebraic closure of the field $\mathbb{K}$                                                          |

| $\mathbb{K}^{\mathbb{N}}$                                     | Set of sequences $(\alpha_n)_{n\in\mathbb{N}}$ with $\alpha_n\in\mathbb{K}$ for all $n\in\mathbb{N}$ |

| $\mathbb{K}[\![Z]\!]$                                         | Ring of the formal power series in Z over $\mathbb{K}$                                               |

| $\mathcal{M}_{m \times n}\left(\mathbb{K}\right)$             | Space of $m \times n$ matrices with coefficients in $\mathbb{K}$                                     |

| (G)                                                           | Ideal generated by the set G                                                                         |

### **Notation of Special Functions**

| #(A)                                   | Cardinality of A                                                                                                                                            |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $char(\mathbb{K})$                     | Characteristic of K                                                                                                                                         |

| $\lfloor x \rfloor$                    | Floor function                                                                                                                                              |

| $\mathcal{V}_{\mathbb{L}}(\mathrm{I})$ | Affine variety of the ideal $I \subseteq \mathbb{K}[X]$ over $\mathbb{L} \supseteq \mathbb{K}$ ; $\mathcal{V}(I) := \mathcal{V}_{\overline{\mathbb{K}}}(I)$ |

| $\sqrt{I}$                             | Radical of the ideal I                                                                                                                                      |

| $\mathfrak{I}(\mathbf{V})$             | Vanishing ideal of the set V                                                                                                                                |

| lc(f)                                  | Leading coefficient of f                                                                                                                                    |

| lm(f)                                  | Leading monomial of f                                                                                                                                       |

| lt(f)                                  | Leading term of f; $lt(f) = lc(f) \cdot lm(f)$                                                                                                              |

| S(f,g)                                 | S-polynomial between f and g                                                                                                                                |

| $A^{\mathrm{T}}$                       | Transpose of the matrix A                                                                                                                                   |

## **Logic Operators**

| $\neg \alpha$                                  | NOT a   |

|------------------------------------------------|---------|

| $a \wedge b$                                   | a AND b |

| $a \lor b$                                     | a OR b  |

| $\boldsymbol{a} \mathrel{\vee} \boldsymbol{b}$ | a XOR b |

List of Symbols

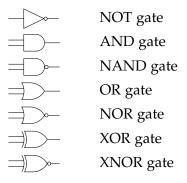

#### **Logic Gates**

Notational Remark. In this work, **boldface** symbols (such as  $\mathfrak a$ ) represent multidimensional objects, like vectors or n-tuples, whereas roman symbols (such as  $\mathfrak a$ ) usually denote one-dimensional values. Variables or unknown quantities are written with lower case letters, while upper case is used for indeterminates in polynomial rings.

### Introduction

A circuit is a set of (logic or arithmetic) gates connected by wires. Its purpose is to implement a function in a way that can be easily realized in the physical world (by means of electronic components like transistors and capacitors).

Suppose that we have a specific function in mind and we want to build a circuit which is able to compute it. We ask a logic designer who gives us the description of the logic gates and their connections. How can we be sure that the circuit does actually do what we want it to do? That is the verification problem, that is to say, the problem of finding a formal proof of the correctness of a circuit.

In this thesis we want to describe some of the algebraic techniques used to solve the verification problem. In particular, we will focus on two main types of methods:

- the *Commutative Algebra* approach, which reduces the problem to the well-known Ideal Membership Problem;

- the Difference Equations approach, which obtains a system of difference equations from the circuit, thus allowing a systematic study from that point of view.

Our starting point is a concrete circuit: a combined Reed-Solomon encoder/syndrome generator proposed by Fettweis and Hassner in [2]. An encoder is a device capable of converting a message into a codeword. Coding theory is a branch of mathematics which develops particular algebraic structures (the codes) which are suitable for transmitting or storing information, because they are able to detect and/or correct possible errors.

In the first chapter we describe briefly how the encoding and the decoding of an RS code work, as well as the circuits to perform those operations. We also introduce the combined encoder/syndrome generator of which we want to prove the correctness.

The second chapter deals with the verification techniques based on commutative algebra. In particular, we follow an article by Lv, Kalla and Enescu [7] which uses the Nullstellensatz for Finite Fields to reduce the verification of a circuit to

xii Introduction

an Ideal Membership Problem. They developed this method for combinational circuits only; we generalize it to include also sequential ones. Moreover, we show another method, based on the vector space structures in play, which is less expensive but works only with linear circuits (whose output depends linearly on the input).

The difference equations are introduced in the third chapter. After a brief description of them, we explain how to translate a circuit into a system of difference equations and illustrate some of the main tools used to study these equations.

In the fourth chapter we employ all these techniques to verify the encoder proposed by Fettweis and Hassner. We begin with particular instances of the circuit, for which we may use the commutative algebra approach. Then we will prove the correctness of the circuit structure, translating it into a system of difference equations, which are more suitable for this kind of proof. We will actually prove that a generalized version of the circuit works.

We conclude hinting at possible further developments of these topics, which may take different paths: we may look for some improvements of the efficiency of the methods shown, or we could analyse the combined circuit more in depth in order to have a better understanding of its functioning, in case that the ideas behind it could be applied in other situations.

### Chapter 1

# Reed-Solomon Encoding and Decoding

In this chapter we are going to describe how a Reed-Solomon (RS) code works. In particular, we will see how to encode a word, turning it into a codeword, and how to perform the actual error correction.

RS codes are usually implemented in technologies which rely on fast information retrieval, such as CD/DVD units and digital television broadcasting. Because of this, researchers and engineers have focused their attention on a hardware implementation rather than a software one. We will present the classical circuits used in encoding/decoding of a RS code, as well as one combined encoder/syndrome calculator presented by Fettweis and Hassner in [2], which reduces the global amount of hardware complexity. A proof of the correctness of this circuit is the main task of this thesis work.

We will assume some basic knowledge of error-correcting codes and logic circuits. A brief summary of these topics can be found respectively in Appendix A and B.

*Notational Remark.* The expression n-word will denote (not so surprisingly) a word of length n.

#### 1.1 How to Encode a Word

Let  $\mathbb{F}_q$  be a finite field with characteristic 2 and let n, k and t be integers such that n = q - 1 and k = n - 2t. Let C be an RS code defined on  $\mathbb{F}_q$  of length n, with an error-correction capacity of t symbols. Thus the encoder takes a word  $w \in (\mathbb{F}_q)^k$  and gives a codeword  $c \in C \subseteq (\mathbb{F}_q)^n$ . We suppose that C is generated

by the polynomial

$$g(X) := \prod_{i=1}^{2t} (X - \alpha^i)$$

where  $\alpha$  is a fixed primitive element of  $\mathbb{F}_q$ .

The Mattson-Solomon polynomial (see Appendix A) defines a method to encode a k-word into an n-codeword, but unfortunately this method isn't systematic.

**Definition 1.1.** An encoding method is *systematic* if the n-codeword is obtained by concatenating the k-word to be encoded with n - k parity-check symbols.

Obviously a systematic method is preferable to a non-systematic one, because it is possible to retrieve the message by truncating the  $\mathfrak{n}-k$  parity-check symbols after the error-correction step, thus avoiding a decoding passage which may be both time- and resources-costing.

In order to systematically encode a k-word  $w(X) = w_0 + w_1 X + \cdots + w_{k-1} X^{k-1}$ , we just need a well-known algorithm: the Euclidean division of polynomials. In fact, the 2t parity-check symbols are just the coefficient of the remainder  $r(X) = r_0 + r_1 X + \cdots + r_{2t-1} X^{2t-1}$  obtained from dividing  $X^{2t}w(X)$  by the generator polynomial g(X), and the codeword is  $c(X) = X^{2t}w(X) + r(X)$ . To see that c belongs to the RS code, notice that  $X^{2t}w(X) = g(X)h(X) + r(X)$  for some c and that c(X) = g(X)h(X) because c char( $\mathbb{F}_q$ ) = 2.

*Example* 1.1. Let us define a 2-error-correcting RS code over  $\mathbb{F}_8$ , which we obtain as  $\mathbb{F}_2[\alpha]$  with  $\alpha^3 + \alpha + 1 = 0$ . It is a code of length 7 with 3 message symbols and 4 parity-check digits, with generator polynomial

$$g(X):=(X-\alpha)(X-\alpha^2)(X-\alpha^3)(X-\alpha^4)$$

A word  $(\beta_2, \beta_1, \beta_0)$  is seen as  $m(X) := \beta_2 X^2 + \beta_1 X + \beta_0$  and its encoding is

$$\mathfrak{m}(X)X^4 + \mathfrak{r}(X) = \beta_2 X^6 + \beta_1 X^5 + \beta_0 X^4 + \gamma_3 X^3 + \gamma_2 X^2 + \gamma_1 X + \gamma_0,$$

where  $r(X) := \gamma_3 X^3 + \gamma_2 X^2 + \gamma_1 X + \gamma_0$  is the remainder of the Euclidean division of  $m(X)X^4$  by g(X). For example, the polynomial  $X^2 + (\alpha + 1)X + (\alpha^2 + \alpha)$  is encoded as

$$X^{6} + (\alpha + 1)X^{5} + (\alpha^{2} + \alpha)X^{4} + (\alpha^{2})X^{2} + (\alpha^{2} + 1)X + \alpha.$$

(1.1)

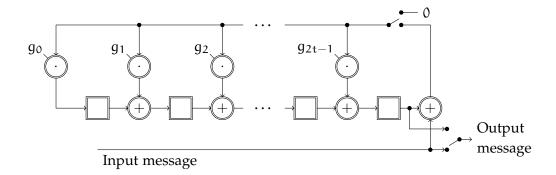

At hardware level, an RS systematic encoder is a division circuit, as shown in

Figure 1.1. In that figure, the symbols  $\rightarrow$  and  $\beta$  represent respectively

Figure 1.1: A standard RS encoder. The  $g_i$ 's are the coefficients of the generator polynomial.

an adder and a multiplier for a fixed  $\beta$ , which operate on elements of  $\mathbb{F}_q$ . The symbol  $\rightarrow$  is a register capable of storing an element of  $\mathbb{F}_q$ , initialized to 0.

At first, and for k clock cycles, the two switches are both in the lower position: the first k symbols of the output word are just the input symbols. After k clock cycles, the registers contain the parity-check symbols, and the switches are activated in order to cut off the input wire and concatenate the parity-check symbols to the output.

#### 1.2 How to Decode a Word

After having received an n-word v(X), we have to decode it, i.e. we have to find the most likely codeword that has been transmitted. This requires a number of steps.

- 1. First of all, we have to compute the syndrome of the word. The 2t symbols of the syndrome are in fact the values  $s_i := \nu(\alpha^i)$ , for i = 1, ..., 2t.

- 2. Then we solve the key equation and retrieve the error locator polynomial  $\sigma(Z)$  and the error evaluator polynomial  $\omega(Z)$ .

- 3. We use  $\sigma(Z)$  and  $\omega(Z)$  to reconstruct the error pattern e(X).

- 4. Finally, we compute the codeword c(X) = v(X) + e(X).

For further information about steps 2. and 3., see Appendix A; we are going to focus our attention just on the first step. Computing syndromes is in fact quite simple; it is a polynomial evaluation, which means that it can be done

by Horner's Algorithm, that is to say, by iterated multiplication and addition, having written

$$v_0 + v_1 X + \cdots + v_{n-1} X^{n-1} = v_0 + X(v_1 + X(v_2 + \cdots + X(v_{n-2} + v_{n-1} X) \dots)).$$

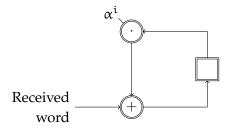

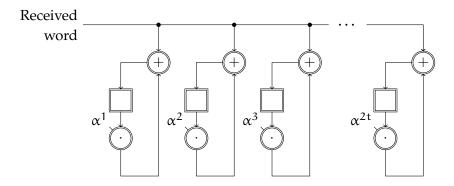

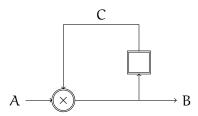

The circuit shown in Figure 1.2 perform this task—the coefficients of v(X), starting

Figure 1.2: Computation of the syndrome  $s_i = v(\alpha^i)$ .

from the leading coefficient, are entered one by one at each clock cycle; when the last one is input, the register stores the value  $s_i$ . A set of 2t units of this circuit allows to compute the values  $s_i$  for  $i=1,\ldots,2t$ .

Figure 1.3: A set of circuit units for syndrome computation.

*Example* 1.2. Continuing from Example 1.1, let's compute the syndrome for the codeword (1.1), which we call w(X). That is not difficult and the result is

$$(w(\alpha), w(\alpha^2), w(\alpha^3), w(\alpha^4)) = (0, 0, 0, 0).$$

Suppose that an error occurred and we received the word

$$\tilde{w}(X) = X^6 + (\alpha + 1)X^5 + (\alpha^2 + 1)X^4 + (\alpha^2)X^2 + (\alpha^2 + 1)X + \alpha$$

(where the only difference is the coefficient of  $X^4$ : in w(X) it was  $\alpha^2 + \alpha$ ). The syndrome is

$$(\tilde{w}(\alpha), \tilde{w}(\alpha^2), \tilde{w}(\alpha^3), \tilde{w}(\alpha^4)) = (1, \alpha^2 + \alpha, \alpha, \alpha^2 + \alpha + 1).$$

From this information we solve the key equation, obtaining

$$\sigma(Z) = 1 + (\alpha^2 + \alpha)Z;$$

$$\omega(Z) = Z.$$

Now,  $\alpha^2 + \alpha = \alpha^4$ , i.e. there have been a single error in the fourth coefficient; from Equation (A.1) we obtain the error pattern

$$e(X) = (\alpha + 1)X^4$$

and finally  $\tilde{w}(X) + e(X) = w(X)$ , successfully correcting the error.

#### 1.3 The Combined RS Encoder/Syndrome Generator

One of the disadvantages of the circuit described in Section 1.1 is that it requires the coefficients of the generator polynomial. Suppose that a change of the code specification is needed, for example because we have to increase the error-correcting capacity. It suffices to add some powers of  $\alpha$ , but this means more multiplier/adder loops in the circuit of Figure 1.1 and, above all, a new computation of the  $g_i$ 's. In other words, we have to rebuild the circuit.

In their article [2], Fettweis and Hassner notice that the encoder and the decoder are rarely active at the same time, thus it is possible to imagine a circuit in which hardware resources are shared between them. By manipulating the standard circuit of Figure 1.1, they managed to describe a combined encoder and syndrome generator for an RS code.

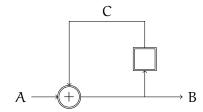

Figure 1.4: The modified RS encoder with a linear feedback loop.

Their main problem was the switch in the feedback loop, which is a nonlinearity that prevented them from applying linear system transformation of the loop itself. However, they realized that, since the characteristic of the coefficient field is 2, the same result could be achieved by assuring that the two inputs of the last adder in the chain were the same, therefore forcing the output of the adder to be 0, as shown in Figure 1.4. The feedback loop is now linear and can be studied by means of linear transformations.

Figure 1.5: The final version of the RS encoder.

Figure 1.5 represents the resulting RS encoder. Notice that the multipliers use the roots of the generator polynomial (i.e. the  $\alpha^i$ 's), and not the coefficients. In fact, there is a strong resemblance between this circuit and the one of Figure 1.3: the only difference is the lower adder chain.

Figure 1.6: The combined encoder/syndrome generator.

The encoder of Figure 1.5 and the syndrome generator of Figure 1.3 can now be combined as shown in Figure 1.6. The "Encode/Decode" wire carries a stream of 1's (for encoding) or 0's (for decoding) of the suitable bandwidth, so that the AND gates let the information pass through the lower adder chain (in case of encoding) or break the chain (in case of decoding). When computing the syndrome, the switch is constantly in the upper position and the output end can be ignored, as the syndrome values will appear in the registers.

The particular structure of this encoder, which uses the  $\alpha^i$ 's instead of the  $g_i$ 's, ensures an easy way to achieve different error-correcting capabilities with the same circuit: it suffices to cut off some of the loops in order to remove the relative  $\alpha^i$  from the generator polynomial, effectively obtaining an encoder for the appropriate RS code.

In the next chapter we will develop a computational algebra method in order to perform the verification of sequential circuits. In particular, we will employ it to confirm that instances of the combined encoder/syndrome generator do actually work.

## Chapter 2

# The Commutative Algebra Approach

One of the most important results in commutative algebra is the so-called *Null-stellensatz*, which relates ideals in the polynomial ring with varieties in the affine space. In this chapter we are going to see how that theorem can be used for the verification of logic circuit.

In particular, we will introduce a verification technique developed by Lv, Kalla and Enescu in [7] for combinational circuits. Starting from there, we will define a generalization of that method in order to be able to deal with sequential circuits. We will call it the *polynomial method*.

We will also show another approach (the *module method*) that is more efficient than the polynomial one, but can be applied only to a specific class of circuits.

#### 2.1 The Nullstellensatz for Finite Fields

Let us recall the basic facts of algebraic geometry. Let  $\mathbb{K}$  be a field and  $\mathbb{K}[X] := \mathbb{K}[X_1, \dots, X_n]$ . For any subset  $\mathcal{P} \subseteq \mathbb{K}[X]$  and any field extension  $\mathbb{L} \supseteq \mathbb{K}$ , we denote by  $\mathcal{V}_{\mathbb{L}}(\mathcal{P})$  the *(affine) variety* of  $\mathcal{P}$  over  $\mathbb{L}$ , that is

$$\mathcal{V}_{\mathbb{L}}(\mathcal{P}) := \{ \alpha \in \mathbb{L}^n \mid \forall p \in \mathcal{P}, \ p(\alpha) = 0 \}.$$

We will omit the subscript for  $\mathbb{L} = \overline{\mathbb{K}}$ . It is easy to show that  $\mathcal{V}_{\mathbb{L}}(\mathcal{P}) = \mathcal{V}_{\mathbb{L}}((\mathcal{P}))$ , so we can consider just ideals instead of generic sets of polynomial.

For any subset  $V \subset \mathbb{K}^n$ , the set of polynomials that vanish on all the points of V forms an ideal, called the *vanishing ideal* of V:

$$\mathfrak{I}(V) := \{ f \in \mathbb{K}[X] \mid \forall \alpha \in V, \ f(\alpha) = 0 \}.$$

**Theorem 2.1** (Weak Nullstellensatz). Let  $\mathbb{K}$  be an algebraically closed field and  $I \subseteq \mathbb{K}[X]$  an ideal. Then  $\mathcal{V}(I) = \emptyset$  if and only if  $I = \mathbb{K}[X]$ .

**Theorem 2.2** (Strong Nullstellensatz). Let  $\mathbb{K}$  be an algebraically closed field and  $I \subseteq \mathbb{K}[X]$  an ideal. Then  $\mathfrak{I}(\mathcal{V}(I)) = \sqrt{I}$ .

There is a little problem: we are going to use finite fields, which are never algebraically closed. For, suppose  $\mathbb{K} = \{q_1, \dots, q_\ell\}$ , the polynomial

$$(X-q_1)\cdot\ldots\cdot(X-q_\ell)+1$$

belongs to  $\mathbb{K}[X]$  but has no root in  $\mathbb{K}$ . This prevents us from applying the Nullstellensatz directly.

What can we do? Actually, there is an elegant solution to our problem. All we have to do is to identify which part of the variety in  $(\overline{\mathbb{F}_q})^n$  lies in fact in  $(\mathbb{F}_q)^n$ , and there is a special polynomial that encodes the elements of  $\mathbb{F}_q$ .

**Proposition 2.3.** All and only the fixed points of the Frobenius automorphism

$$\begin{array}{ccc} \phi_q \colon \ \overline{\mathbb{F}_q} & \longrightarrow & \overline{\mathbb{F}_q} \\ x & \longmapsto & x^q \end{array}$$

are the elements of  $\mathbb{F}_q$ . In other words, the roots of the polynomial  $X^q - X$  are the elements of  $\mathbb{F}_q$ .

As a consequence, we may hope that adding relations of the form  $X_i^q - X_i$  (which we will call *field equations*) would help us solve the problem. In fact, that is what happens, as stated in the following theorems.

**Theorem 2.4** (Weak Nullstellensatz over Finite Fields). Let  $I \subseteq \mathbb{F}_q[X]$  be an ideal, and  $I_0 := (X_1^q - X_1, \dots, X_n^q - X_n)$ . Then  $\mathcal{V}_{\mathbb{F}_q}(I) = \emptyset$  if and only if  $(I, I_0) = \mathbb{F}_q[X]$ .

*Proof.* Let  $\overline{\mathbb{F}_q}$  denote the algebraic closure of  $\mathbb{F}_q$  and let  $\mathcal{V}(I)$  be the variety of I over  $\overline{\mathbb{F}_q}$ . We have  $\mathcal{V}_{\mathbb{F}_q}(I) = \mathcal{V}(I) \cap (\mathbb{F}_q)^n$ . Now,  $(\mathbb{F}_q)^n$  is a finite set of points, so it is  $\mathcal{V}(I_0)$  for some  $I_0$ . It follows that

$$\mathcal{V}_{\mathbb{F}_q}(I) = \mathcal{V}(I) \cap (\mathbb{F}_q)^n = \mathcal{V}(I) \cap \mathcal{V}(I_0) = \mathcal{V}(I, I_0). \tag{2.1}$$

We have only to prove that  $I_0 = (X_1^q - X_1, \dots, X_n^q - X_n)$ , but this is a straightforward consequence of Proposition 2.3.

**Lemma 2.5.** For any ideal  $I \subseteq \mathbb{F}_q[X]$ , the ideal  $(I, I_0)$  is radical.

*Proof.* Since any ideal is contained in its radical, we only have to prove that

$$\sqrt{(I,I_0)} \subseteq (I,I_0)$$

.

Let  $f \in \sqrt{(I, I_0)}$ . This means there is an  $s \in \mathbb{N}$  such that  $f^s \in (I, I_0)$ . Now let [f] and [I] be the classes of f and I in  $\mathbb{F}_q[X]/I_0$ . We have  $[f]^s \in [I]$ , and it suffices to prove that  $[f] \in [I]$ .

Firstly we show that, for any  $[g] \in \mathbb{F}_q[X]/I_0$ ,  $[g]^q = [g]$ . This can be done by induction on the number of terms in g.

- 1. If  $[g] = [cX^{\alpha}]$  is a monomial, then  $[g]^q = [c^qX^{q\alpha}] = [cX^{\alpha}] = [g]$ .

- 2. Suppose  $[g] = [h_1] + [h_2]$ . By inductive hypothesis  $[h_1]^q = [h_1]$  and  $[h_2]^q = [h_2]$ . Then

$$[g]^{q} = ([h_{1}] + [h_{2}])^{q} = \sum_{i=0}^{q} {q \choose i} [h_{1}]^{i} [h_{2}]^{q-i} =$$

$$= [h_{1}]^{q} + [h_{2}]^{q} = [h_{1}] + [h_{2}] = [g].$$

Since  $[f]^q = [f]$ , without loss of generality we may assume s < q. But now  $[f]^s \in [I]$  and also

$$[f]^{s}[f]^{q-s} = [f]^{q} = [f] \in [I].$$

This ends the proof.

**Theorem 2.6** (Strong Nullstellensatz over Finite Fields). *Let*  $I \subseteq \mathbb{F}_q[X]$  *be an ideal. Then*  $\mathfrak{I}(\mathcal{V}_{\mathbb{F}_q}(I)) = (I, I_0)$ .

*Proof.* By the Strong Nullstellensatz applied to the ideal (I, I<sub>0</sub>) and Lemma 2.5, we have

$$\mathfrak{I}(\mathcal{V}(I,I_0)) = (I,I_0).$$

The thesis follows by Relation (2.1).

#### 2.2 Verification of Combinational Circuits

In this section we will describe the verification technique developed by Lv, Kalla and Enescu in [7]. They use the results of the previous section to translate the verification problem in an ideal membership problem, which can be effectively solved using standard algebraic methods. They focus on *combinational* circuits only, where the output is a polynomial function of the input.

We begin with what we want the circuit to do. For example, we may want to build a multiplier over  $\mathbb{F}_4$ , i.e. a circuit that takes  $a, b \in \mathbb{F}_4$  and gives  $ab \in \mathbb{F}_4$ .

We encode the relation between input and output in a multivariate polynomial (*specification polynomial*)  $f(Z, A_1, ..., A_k)$ , where Z and  $A_1, ..., A_k$  are variables representing the output and the inputs respectively. In our example, we have f(Z, A, B) = Z - AB.

Then we have the *implementation* of the circuit, which is the information about the number and the type of logic gates needed, and their disposition in the circuit. The gates are modelled with the standard correspondence between Boolean algebras and Boolean rings, which can be found in Table 2.1. In addition

| Boolean expression | Ring operation      |

|--------------------|---------------------|

| ¬a                 | $1 + \alpha$        |

| $a \wedge b$       | $a \cdot b$         |

| $a \lor b$         | $a \cdot b + a + b$ |

| $a \vee b$         | a + b               |

Table 2.1: Translation between Boolean expression and ring operation in a Boolean algebra.

to these, we have to include any other relation between the variables appearing in the specification polynomial and the variables which arise from the description of the circuit.

An example of a multiplier over  $\mathbb{F}_4$  is given in Figure 2.1.

Figure 2.1: A two-bit multiplier over  $\mathbb{F}_4$ .

All the variables in Figure 2.1 may assume a binary value. The result of the

polynomial translation is shown in Table 2.2.

| Gate           | Polynomial Expression |

|----------------|-----------------------|

| f <sub>1</sub> | $C_0 - A_0 B_0$       |

| $f_2$          | $C_3 - A_1B_1$        |

| $f_3$          | $C_2 - A_1 B_0$       |

| $f_4$          | $C_1 - A_0B_1$        |

| $f_5$          | $Z_0 - (C_0 + C_3)$   |

| $f_6$          | $Z_1 - (C_3 + R_0)$   |

| $f_7$          | $R_0 - (C_2 + C_1)$   |

Table 2.2: Polynomial translation of the gates of Figure 2.1.

We also have to link the specification variables and the input/output of the circuit. In this example, we assume that  $\mathbb{F}_4$  is given as  $\mathbb{F}_2[\alpha]$  where  $\alpha^2 + \alpha + 1 = 0$ . The relations between Z, A, B and the variables appearing in the circuit are

$$f_8: A - (A_0 + A_1 \alpha), \qquad f_9: B - (B_0 + B_1 \alpha), \qquad f_{10}: Z - (Z_0 + Z_1 \alpha).$$

Now, what does "the circuit works" mean? All the polynomial obtained from the implementation generate an ideal I in a suitable polynomial ring. A point of  $\mathcal{V}_{\mathbb{F}_q}(I)$  describes a way to assign values to the polynomial variables which comply with the circuit constraints. To verify the correctness of the circuit, we have to test whether these values also agree with the specification polynomial f, that is to say, whether f vanishes on all points of  $\mathcal{V}_{\mathbb{F}_q}(I)$ . By Theorem 2.6, this can be done by checking if  $f \in (I, I_0)$ . Notice also that if there is a point  $\mathbf{p} \in \mathcal{V}_{\mathbb{F}_q}(I)$  such that  $f(\mathbf{p}) \neq 0$ , we are sure that there is a bug in the design.

The steps of the verification algorithm are now clear:

- 1. deduce the set of polynomials I corresponding to the circuit instance;

- 2. append to these the suitable field equations I<sub>0</sub>;

- 3. compute a Gröbner basis  $\mathcal{G}$  of  $I \cup I_0$ ;

- 4. reduce the specification polynomial f with respect to 9;

- 5. if the output is 0, the circuit is correct; otherwise, there is a bug in the design.

In the rest of their article, Lv, Kalla and Enescu explain some techniques that improve the efficiency of the algorithm. In particular,

- they describe how to choose a monomial ordering such that the set of polynomial obtained in step 1. above is already a Gröbner basis, thus eliminating the need of computing one with Buchberger's Algorithm;

- they use an improved reduction approach based on Faugère's F<sub>4</sub> Algorithm, which has overall better performances.

#### 2.3 Dealing with Time: the Polynomial Method

In the last section we focused our attention on combinational circuits, following [7]. What we want to do now is try to take time into account, that is to say, we want to generalize that method in order to obtain a way to verify sequential circuits.

Let us consider a memory register. From Appendix B we know that it is a device capable of storing data. It changes its state at every clock cycle, updating its content according to its input terminal.

How can we represent a situation like this? It is not hard to imagine that we may label each polynomial variable with an integer index, which states the clock cycle at which we are considering the variable. In other words, we encode the information in the i-th wire of the circuit at time j in a variable  $X_{ij}$  of the polynomial ring. Obviously this brings to polynomial rings with a huge number of variables.

In this setting, every (combinational) logic gate  $f(X_1,...,X_k)$  has to be repeated for each time: the ideal describing the circuit contains  $f(X_{1j},...,X_{kj})$  for all j. (Notice that we are assuming that the number of clock cycles required by the circuit is known in advance.) A memory register with input D and output Q is represented by the set of polynomials  $Q_{j+1} - D_j$ , meaning "the output at time j+1 is equal to the input at time j". The polynomial  $Q_1 - \beta$  is added to the set, representing the initial condition of the register (at time 1 the value  $\beta$  is stored).

A point in the variety  $\mathcal{V}_{\mathbb{F}_q}(I)$  now encodes the possible values for the variables according not only to the circuit constraints but also to the evolution in time. Correctness of the design is achieved by assuring that the specification polynomial (also modelled taking time into account) vanishes on all the points of  $\mathcal{V}_{\mathbb{F}_q}(I)$ .

*Example* 2.1. We want to build a circuit that takes one value  $a_i \in \mathbb{F}_q$  at each clock cycle and, after n cycles, returns  $a_1 \cdot \ldots \cdot a_n$ . The circuit shown in Figure 2.2 is a good candidate. The gate  $\xrightarrow{}$  multiplies two elements of  $\mathbb{F}_q$ . The inputs are given in the wire A and we expect the output from wire B. The register is set to 1 in the beginning.

Figure 2.2: A recursive multiplier over  $\mathbb{F}_q$ .

To have an instance of the circuit, let us set n = 5. The polynomial ring in which we are working is

$$R := \mathbb{F}_q[A_1, A_2, A_3, A_4, A_5, B_1, B_2, B_3, B_4, B_5, C_1, C_2, C_3, C_4, C_5].$$

The specification polynomial is  $f: B_5 - A_1A_2A_3A_4A_5$ . Let us model the gates.

**The multiplier.** The polynomials are  $B_i - A_i C_i$  for each i = 1, ..., 5.

**The register.** At first the register contains 1, so we have  $C_1 - 1$ ; then, for i = 2, ..., 5, we derive  $C_i - B_{i-1}$ .

To these we have to add the field equations  $\ell_i^q - \ell_i$  for each  $\ell \in \{A,B,C\}$  and  $i=1,\ldots,5.$

We choose  $\mathbb{F}_8$  for a test with the software Sage. At first we define  $\mathbb{F}_8$  and R with

#### Then we define the ideal

#### and the specification polynomial

```

f=B5-A1*A2*A3*A4*A5;

```

The result of f.reduce(I.groebner\_basis()) is 0, thus we may conclude that the circuit works.

#### 2.4 Dealing with Time: the Module Method

The polynomial method has a major drawback in the fact that it requires rings with a lot of variables, which usually means high computational cost. In this section we try to overcome this problem by choosing another mathematical structure to represent the evolution of the circuit in time. Unfortunately, the price we have to pay is a loss of generality—this other method can be used only for a special class of circuits (which includes the combined RS encoder/syndrome generator of Chapter 1).

At first we thought to employ *modules* instead of rings. The environment is the module  $\mathbb{K}[X]^T = \mathbb{K}[X_1, \dots, X_n]^T$ , where  $X_1, \dots, X_n$  represent wires and T is the number of clock cycles. The j-th component represents the j-th cycle. In other words, if  $(e_1, \dots, e_T)$  is the canonical basis of  $\mathbb{K}[X]^T$  (as a  $\mathbb{K}[X]$ -module), the term  $X_i e_i$  stores the information of the i-th wire at time j.

Now it is easy to understand why only particular circuits can be verified with this method. For example, the recursive multiplier of Figure 2.2  $\mathit{can't}$  be tested: the specification polynomial would contain expressions like  $(Ae_1) \cdot \ldots \cdot (Ae_k)$  which have no meaning in this context. The suitable circuits for this method are the  $\mathit{linear}$  ones, that is to say, their output is a  $\mathbb{K}$ -linear combination of their inputs.

This brought us to redefine the method: the underlying sets remain the same, but now they are regarded as  $\mathbb{K}$ -vector spaces instead of  $\mathbb{K}[X]$ -modules.

The circuit is modelled as a  $\mathbb{K}$ -vector subspace of  $\mathbb{K}[X_1, \dots, X_n]^\mathsf{T}$  generated by its constraints, which are derived with the following rules.

- Every combinatorial logic gate has to be repeated for each component (i.e. we have  $f(X_1,...,X_n)e_j$  for all j=1,...,T). This means that for every logic gate  $f(X_1,...,X_n)$  the columns of  $f(X_1,...,X_k)I_T$ , where  $I_T$  is the  $T \times T$  identity matrix, belong to the subspace defining the circuit.

- A memory register with input D and output Q is described by the T 1 vectors  $Qe_{j+1} De_j$  (for j = 1, ..., T 1) and the initialization vector  $(Q \beta)e_1$  if the register stores  $\beta$  as its initial value.

The specification polynomial now becomes a *specification vector*, built in the same way as in the polynomial method (with the obvious substitutions), and we have to test its membership to the subspace defined by the circuit.

**Theorem 2.7.** Let  $M \subseteq \mathbb{K}[X]^T$  be the  $\mathbb{K}$ -subspace generated by the circuit units (as well as any other relation that is used by the polynomial method, such as the field equations), and let  $f \in \mathbb{K}[X]^T$  be the specification vector. If  $f \in M$ , the circuit works.

*Proof.* In this proof, we will use the following notation:

- $X = \{X_1, ..., X_n\}$  will denote the set of the wire variables, without any reference to time;

- X<sub>j</sub> := {X<sub>ij</sub> | i = 1,...,n} is the set of the wire variables with a (fixed) time index j, which ranges from 1 to the number T of clock cycles required by the circuit;

- $\bullet \ X^* := X_1 \cup \cdots \cup X_T.$

We define the  $\mathbb{K}$ -linear map  $\Psi \colon \mathbb{K}[X]^T \to \mathbb{K}[X^*]$  as

$$\mathbb{K}[X]^{\mathsf{T}} \longrightarrow \bigoplus_{j=1}^{\mathsf{T}} \mathbb{K}[X_j] \longrightarrow \mathbb{K}[X^*]$$

$$\begin{pmatrix} f_1(X) \\ \vdots \\ f_T(X) \end{pmatrix} \longmapsto \begin{pmatrix} f_1(X_1) \\ \vdots \\ f_T(X_T) \end{pmatrix} \longmapsto \sum_{j=1}^{\mathsf{T}} f_j(X_j).$$

In other words, the first map simply renames the variables of  $f_j$  adding the time index j, and the second map sums all the components.

Suppose that M is generated by the (finite) circuit relations  $v_1, \ldots, v_m$ . Our claims are that

- 1.  $\Psi(f)$  and  $\Psi(v_1), \dots, \Psi(v_m)$  are respectively the specification polynomial and the polynomials representing the gates and registers for the polynomial method;

- 2. if  $f \in M$ , then  $\Psi(f)$  belongs to the ideal generated by  $\Psi(\nu_1), \dots, \Psi(\nu_m)$ , thus proving the correctness of the circuit by the polynomial method of Section 2.3.

For j = 1,...,T let  $e_j$  be the vector with 1 in the j-th component and 0 elsewhere. The first claim follows directly by definition of  $\Psi$ . Here are some examples:

- if g(X) represents a combinational logic gate, we have  $g(X)e_j$  for each j = 1, ..., T, whose image under  $\Psi$  is  $g(X_j)$ ;

- a register with input D and output Q is modelled by Qe<sub>j+1</sub> De<sub>j</sub>, which

is sent to Q<sub>j+1</sub> D<sub>j</sub> by Ψ.

The second claim is clear too, because of the linearity of  $\Psi$ : suppose that  $f \in M$  and write

$$f = \sum_{i=1}^{m} \beta_i v_i$$

for  $\beta_1, \ldots, \beta_m \in \mathbb{K}$ . Then

$$\Psi(\mathbf{f}) = \sum_{i=1}^m \beta_i \Psi(\nu_i) \in (\Psi(\nu_1), \dots, \Psi(\nu_m)).$$

This completes the proof.

*Example* 2.2. We slightly modify the circuit of Figure 2.2 so that now it recursively *adds* instead of multiply.

Figure 2.3: A recursive adder over  $\mathbb{F}_q$ .

This time the register is set to 0 at first. We choose for example  $\mathfrak{n}=5$  and obtain the relations

$$\mathbf{A} := \begin{pmatrix} B - (A + C) & 0 & 0 & 0 & 0 \\ 0 & B - (A + C) & 0 & 0 & 0 \\ 0 & 0 & B - (A + C) & 0 & 0 \\ 0 & 0 & 0 & B - (A + C) & 0 \\ 0 & 0 & 0 & 0 & B - (A + C) \end{pmatrix}$$

for the adder, and

$$\mathbf{R} := \begin{pmatrix} C & -B & 0 & 0 & 0 \\ 0 & C & -B & 0 & 0 \\ 0 & 0 & C & -B & 0 \\ 0 & 0 & 0 & C & -B \\ 0 & 0 & 0 & 0 & C \end{pmatrix}$$

for the register. (We should add also the field equations, but in this simple example they are irrelevant.) The specification vector is

$$f := \begin{pmatrix} -A \\ -A \\ -A \\ -A \\ B - A \end{pmatrix}.$$

We have to check whether f belongs to the subspace of the  $\mathbb{K}$ -linear combinations of the columns of A and R. A quick computation, in fact, tells us that

$$f = a_1 + a_2 + a_3 + a_4 + a_5 + r_1 + r_2 + r_3 + r_4 + r_5$$

(where the  $a_i$ 's and the  $r_i$ 's are the columns of A and R), thus establishing the correctness of the circuit.

#### 2.5 A First Result: Arbitrariness of the Coefficient Field

In this section we are going to show that, if the circuit specification and the constraints are modelled with linear polynomials, a correctness proof based on the polynomial method will be valid independently of the underlying field of coefficients—under the obvious assumption that the adders and the scalar multipliers of a particular instance of the circuit are designed to operate with elements of the suitable field.

Remember that the information about our working field is given by the field equations, which are polynomials like  $X_i^q - X_i$ . The field equations have to be appended to the ideal generated by the circuit constraints in order to trigger the Nullstellensatz over Finite Fields. The question is, do we really need them? Generally speaking, the answer is yes: there are examples in which their absence brings to wrong results. The situation is different when we are dealing with linear polynomials.

Recall that there are some useful criteria that avoid some computation when looking for a Gröbner basis. We will report here just one of them; its proof can be found, for example, in [1].

**Proposition 2.8** (Product Criterion). Let  $f, g \in \mathbb{K}[X_1, ..., X_n]$  be polynomials such that lt(f) and lt(g) are coprime. Then their S-polynomial S(f, g) reduces to 0.

**Lemma 2.9.** The S-polynomial between two linear polynomials either reduces to 0 or is linear. Moreover, reducing a linear polynomial with other linear polynomials results in a linear polynomial.

*Proof.* A linear polynomial  $f \in \mathbb{K}[X_1, \dots, X_n]$  may be written as

$$f(X) = \alpha_1 X_1 + \cdots + \alpha_n X_n + \alpha_0.$$

Let f and g be linear polynomials, with  $lt(f) = \alpha_i X_i$  and  $lt(g) = \beta_j X_j$ .

• If  $i \neq j$ , the two leading terms are coprime, hence S(f,g) reduces to 0 by the Product Criterion.

• If i = j, suppose  $lt(f) = \alpha_i X_i$  and  $lt(g) = \beta_i X_i$ , then  $S(f, g) = \beta_i f - \alpha_i g$  is a linear polynomial.

As far as reduction is concerned, a linear polynomial f can be reduced by another linear polynomial g only if lm(g) appears among the monomials of f; in that case, supposing that  $lt(g) = \beta_i X_i$  and that there is  $\alpha_i X_i$  in f, reduction of f by g results in  $f - (\alpha_i/\beta_i)g$ , which is a linear polynomial.

Now, the polynomial method requires an ideal membership test in order to prove the correctness of the circuit. In particular, for linear circuits we have to check whether a linear specification polynomial belongs to an ideal generated by other linear polynomials and the field equations. But the field equations are not linear, which means they will never participate during the reduction step of the algorithm, because of their high degree. Thus, it is possible to change them with other field equations without affecting the passages of the membership test.

This proves that changing the field of the coefficients (i.e. changing the field equations) doesn't modify the outcome of the test. We conclude that the polynomial method can be used for testing correctness of circuits whose constraints are given by linear polynomials, without having to fix a field for the coefficients.

However, we have to be very careful when applying the principle stated above. The field equations, in fact, limit the values that the variables may take; they don't affect the coefficient field directly. This means that, if the circuit is designed to work with specific constraints over the coefficients (e.g. only in characteristic 2), the field has to fulfil these requirements.

## **Chapter 3**

# The Difference Equations Approach

The commutative algebra techniques analysed in Chapter 2 can be applied when the number of clock cycles is known in advance. In this chapter we try to change our point of view: we translate the behaviour of the circuit into a system of difference equations. These equations relate the state and the output at time k with the state and the input at time k-1; as a consequence, it is not necessary to know the number of steps in advance, because we can proceed one step at a time.

We will consider only linear difference equations, because the RS encoder we are going to study is a linear circuit. Thus, the methods that we are going to show are not suitable for other types of circuits.

#### 3.1 Difference Equations

A difference equation may be seen as a sort of "discrete differential equation", that is to say, it is a relation that expresses the evolution in time of a discrete function (i.e. a sequence).

**Definition 3.1.** A (*linear*) difference equation of order k with coefficients in  $\mathbb{K}$  is a relation of the form

$$\sum_{j=0}^{k} h_{j} a_{i+j} = 0, \tag{3.1}$$

where  $i \in \mathbb{N}$ ,  $h_j \in \mathbb{K}$ ,  $h_0 \neq 0$ ,  $h_k = 1$  and the  $\alpha_i$ 's are unknowns. A *solution* of the difference equation is a sequence  $(\alpha_i)_{i \in \mathbb{N}} \in \mathbb{K}^{\mathbb{N}}$  whose terms satisfy (3.1).

It is not difficult to show that the set of all solutions of a difference equation of order k is a k-dimensional  $\mathbb{K}$ -linear subspace of  $\mathbb{K}^{\mathbb{N}}$ . In fact, for each

$(b_0,\ldots,b_{k-1})\in\mathbb{K}^k$  there exists a unique solution  $(a_i)_{i\in\mathbb{N}}$  such that  $a_0=b_0,\ldots,a_{k-1}=b_{k-1}$ .

**Definition 3.2.** Let  $\sum h_j a_{i+j} = 0$  be a difference equation of order k. The polynomial

$$h(T) := \sum_{j=0}^{k} h_j T^j$$

is called *characteristic polynomial* of the equation.

The roots of the characteristic polynomial play an important role in determining a so-called *closed form* of a solution, that is an expression of the n-th term  $a_n$  that depends on n only, and not on the previous terms. Let  $\alpha$  be a root of h(T) in a suitable algebraic extension of  $\mathbb{K}$ . Then the sequence  $(\alpha^n)_{n\in\mathbb{N}}$  obviously satisfies the difference equation. Assuming that the roots of h(T) are distinct (let them be  $\alpha_1, \ldots, \alpha_k$ ), linearity implies that for any  $\mathbb{K}$ -linear combination

$$s_n := y_1 \alpha_1^n + \dots + y_k \alpha_k^n, \quad y_1, \dots, y_k \in \mathbb{K}$$

the sequence  $(s_n)_{n\in\mathbb{N}}$  is a solution of the equation.

*Example* 3.1. The Fibonacci numbers are generated by the second order difference equation (with coefficients in  $\mathbb{R}$ )

$$a_{i+2} = a_{i+1} + a_i \tag{3.2}$$

along with the initial conditions  $a_0=0$ ,  $a_1=1$ . The characteristic polynomial is  $h(T)=T^2-T-1$ , whose roots are

$$\frac{1+\sqrt{5}}{2} \quad \text{and} \quad \frac{1-\sqrt{5}}{2}.$$

The set of the solutions of Equation (3.2) is

$$\left\{ \left( y_1 \left( \frac{1+\sqrt{5}}{2} \right)^n + y_2 \left( \frac{1-\sqrt{5}}{2} \right)^n \right)_{n \in \mathbb{N}} \middle| y_1, y_2 \in \mathbb{R} \right\}.$$

By imposing the initial condition

$$\begin{cases} y_1 + y_2 = 0 \\ y_1 \left( \frac{1 + \sqrt{5}}{2} \right) + y_2 \left( \frac{1 - \sqrt{5}}{2} \right) = 1 \end{cases}$$

and solving the system, we obtain the well-known formula for the Fibonacci numbers

$$\alpha_n = \frac{1}{\sqrt{5}} \left(\frac{1+\sqrt{5}}{2}\right)^n - \frac{1}{\sqrt{5}} \left(\frac{1-\sqrt{5}}{2}\right)^n.$$

3.2. The Z-Transform 23

So, how can a sequential circuit be translated into a difference equation? There are three important sequences related to a generic sequential circuit:

- the *input* sequence  $(u(t))_{t\in\mathbb{N}}$ ;

- the *state* sequence  $(x(t))_{t\in\mathbb{N}}$ ;

- the *output* sequence  $(y(t))_{t \in \mathbb{N}}$ .

Each sequence contains information about the input, state and output of the circuit at every clock cycle t. The behaviour of a linear circuit is encoded in two difference equations:

$$\begin{cases} x(t+1) = Ax(t) + Bu(t) \\ y(t) = Cx(t) + Du(t) \end{cases}$$

(3.3a) (3.3b)

where A, B, C, D are constants determined by the circuit constraints. Equation (3.3a) tells us how the state changes in function of the current state and input; Equation (3.3b) express the output in terms of the state and the input. Notice that both equations are linear.

All the objects in Equations (3.3) may be scalars, vectors or matrices, depending on the particular circuit, if those representations are more suitable. The dimensions of the constants are chosen in order to preserve the equations' consistency.

Once translated into a system of difference equations, a circuit can be studied from that point of view. For example, we may know *a priori* how the output y(t) is related to the input u(t), so that we just have to check if these sequences satisfy Equations (3.3). In the following sections we will describe some tools used to analyse difference equations.

#### 3.2 The Z-Transform

A difference equation talks about sequences; we may enter the realm of Algebra turning those sequences into algebraic objects.

**Definition 3.3.** Let  $\mathfrak{a}=(\mathfrak{a}_n)_{n\in\mathbb{N}}\in\mathbb{K}^\mathbb{N}$  be a sequence. The *Z-transform* of  $\mathfrak{a}$ , denoted by  $\mathfrak{Z}[\mathfrak{a}]$ , is the formal power series

$$\mathbb{Z}[\mathfrak{a}] := \sum_{n=0}^{\infty} \mathfrak{a}_n \mathsf{Z}^{-n} \in \mathbb{K}[\![\mathsf{Z}^{-1}]\!].$$

Table 3.1 shows some Z-transforms for some of the basic sequences. Besides the definition, there are some tools that allow to compute Z-transforms from other known ones.

| Name               | Definition                                                                             | Z-transform                                  |

|--------------------|----------------------------------------------------------------------------------------|----------------------------------------------|

| Discrete impulse   | $\delta_0(n) = \begin{cases} 1 & \text{if } n = 0 \\ 0 & \text{otherwise} \end{cases}$ | $\mathcal{Z}[\delta_0] = 1$                  |

| Discrete step      | $h_n=1 \ \forall n \in \mathbb{N}$                                                     | $\mathfrak{Z}[\mathbf{h}] = \frac{Z}{Z - 1}$ |

| Geometric sequence | $g_n = \alpha^n$                                                                       | $\mathfrak{Z}[g] = \frac{Z}{Z - \alpha}$     |

Table 3.1: Some common sequences with their Z-transforms.

**Proposition 3.4** (Linearity of Z-Transform). For any  $a,b \in \mathbb{K}^{\mathbb{N}}$  and  $\alpha,\beta \in \mathbb{K}$ , we have

$$\mathcal{Z}[\alpha \mathbf{a} + \beta \mathbf{b}] = \alpha \mathcal{Z}[\mathbf{a}] + \beta \mathcal{Z}[\mathbf{b}].$$

*Proof.* It follows immediately from the  $\mathbb{K}$ -vector space structure of  $\mathbb{K}^{\mathbb{N}}$  and  $\mathbb{K}[X^{-1}]$ .

**Proposition 3.5** (Forward Shift Operator). Let  $\mathfrak{a} = (\mathfrak{a}_n)_{n \in \mathbb{N}}$  be a sequence. Define the forward shift operator  $\mathcal{F} \colon \mathbb{K}^{\mathbb{N}} \to \mathbb{K}^{\mathbb{N}}$  as

$$(\mathcal{F}(\mathfrak{a}))_n := \mathfrak{a}_{n+1} \qquad \forall n \in \mathbb{N}.$$

Then

$$\mathcal{Z}[\mathcal{F}(\mathbf{a})] = Z \mathcal{Z}[\mathbf{a}] - Z \mathbf{a}_0.$$

*Proof.* This is a straightforward computation, isolating the first term of the series  $Z \mathcal{Z}[\mathfrak{a}]$ .

**Proposition 3.6** (Backward Shift Operator). Let  $\mathfrak{a} = (\mathfrak{a}_n)_{n \in \mathbb{N}}$  be a sequence. Define the backward shift operator  $\mathcal{B} \colon \mathbb{K}^{\mathbb{N}} \to \mathbb{K}^{\mathbb{N}}$  as

$$(\mathcal{B}(\mathbf{a}))_n := egin{cases} a_{n-1} & \textit{for } n \neq 0, \\ 0 & \textit{for } n = 0. \end{cases}$$

Then

$$\mathcal{Z}[\mathcal{B}(\alpha)] = Z^{-1} \mathcal{Z}[\alpha].$$

*Proof.* It suffices to collect a  $Z^{-1}$  from  $\mathfrak{Z}[\mathcal{B}(\mathfrak{a})]$ .

### 3.3 Transfer Functions

Let us consider a system of difference equations associated to a circuit

$$\begin{cases} x(t+1) = Ax(t) + Bu(t) \\ y(t) = Cx(t) + Du(t) \end{cases}$$

with  $x(0) = x_0$ . We compute the Z-transforms of all the sequences appearing in those equations. Let  $\mathfrak{X}(Z) := \mathfrak{Z}[x(t)]$ ,  $\mathfrak{Y}(Z) := \mathfrak{Z}[y(t)]$  and  $\mathfrak{U}(Z) := \mathfrak{Z}[u(t)]$ . Linearity and forward shift rule lead to

$$\begin{cases} ZX(Z) - Zx_0 = AX(Z) + BU(Z) \\ Y(Z) = CX(Z) + DU(Z) \end{cases}$$

and a simple manipulation gives

$$\begin{cases} \mathfrak{X}(Z) = Z(ZI-A)^{-1}x_0 + (ZI-A)^{-1}B\mathfrak{U}(Z) \\ \mathfrak{Y}(Z) = ZC(ZI-A)^{-1}x_0 + (C(ZI-A)^{-1}B+D)\mathfrak{U}(Z) \end{cases}$$

where I is an identity matrix of appropriate dimension.

**Definition 3.7.** The *transfer function* of a circuit is the ratio

$$G(Z) := C(ZI - A)^{-1}B + D$$

between the Z-transform of the output and the Z-transform of the input for the initial state  $x_0 = 0$ .

Notice that the transfer function does not depend on the particular input, but only on the linear system that we are studying.

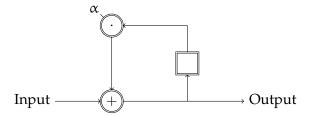

*Example* 3.2. Let's compute the transfer function of a single unit of the syndrome generator, like the one of Figure 1.2. In this case, input and output symbols are

Figure 3.1: The same of Figure 1.2.

managed one at a time, and there is just one register, so the sequences x(t), y(t) and u(t) are all 1-dimensional.

Now, let's follow the wires. The content of the register is multiplied by  $\alpha$ , then added to the input, and the result is given as output; the difference equation that models this behaviour is

$$y(t) = \alpha x(t) + u(t).$$

The same output wire is also the one which updates the register, so we have

$$x(t+1) = \alpha x(t) + u(t).$$

In other words, this circuit has  $A=C=\alpha$  and B=D=1. The transfer function is then

$G(Z) = 1 + \frac{\alpha}{Z - \alpha} = \frac{Z}{Z - \alpha}.$

### 3.4 Circuit Equivalence

Besides verifying a circuit correctness, the difference equations may also test the equivalence of two linear circuits.

**Definition 3.8.** Two circuits described by the systems

$$\begin{cases} x(t+1) = Ax(t) + Bu(t) \\ y(t) = Cx(t) + Du(t) \end{cases} \quad \text{and} \quad \begin{cases} w(t+1) = \tilde{A}w(t) + \tilde{B}u(t) \\ y(t) = \tilde{C}w(t) + \tilde{D}u(t) \end{cases}$$

are algebraically equivalent if there exists an invertible linear transformation T such that x(t) = Tw(t) for all t and

$$\begin{split} \tilde{A} &= T^{-1}AT, & \tilde{B} &= T^{-1}B, \\ \tilde{C} &= CT, & \tilde{D} &= D. \end{split}$$

It is easy to show that two algebraically equivalent circuits are "equivalent" in the sense that they produce the same outputs if their input is the same. In fact, from the second circuit we have

$$\begin{cases} w(t+1) = T^{-1}ATw(t) + T^{-1}Bu(t) \\ y(t) = CTw(t) + Du(t) \end{cases}$$

and, multiplying by T on the left the first equation and writing x(t) = Tw(t), we obtain the equations of the first circuit.

As we may expect, since the transfer function depends on the behaviour of a circuit, two algebraically equivalent circuits have also the same transfer function:

$$\begin{split} \tilde{G}(Z) &= \tilde{C}(ZI - \tilde{A})^{-1} \tilde{B} + \tilde{D} = \\ &= CT(ZT^{-1}IT - T^{-1}AT)T^{-1}B + D = \\ &= CTT^{-1}(ZI - A)^{-1}TT^{-1}B + D = \\ &= C(ZI - A)^{-1}B + D = G(Z). \end{split}$$

# Chapter 4

# Correctness of the Combined RS Encoder/Syndrome Generator

In this chapter we will apply the methods described in the previous chapters in order to prove that the combined RS encoder/syndrome generator of Chapter 1 is correct. In the "decode" mode, the circuit reduces to the standard syndrome generator of Figure 1.3, so we will consider the "encode" mode only.

At first we will fix a length and an error capability of the RS code and we will verify an instance of the circuit with those parameters using the polynomial method. Then we will translate the general circuit into a system of difference equations and will work on them, in order to prove that the encoder is correct for any choice of the parameters.

#### 4.1 Particular Instances of the Circuit

The polynomial method requires all the circuit parameters to be known in advance. It is useful when we have a particular instance of the circuit and we want to test its correctness. Unfortunately, it relies on actual computations, which means we can't leave a literal parameter (such as 2t, the number of check symbols). In other words, this method is unable to prove the correctness of the circuit *structure*—it verifies single instances.

#### 4.1.1 2-Error-Correcting RS over $\mathbb{F}_8$

Let us begin with the 2-error-correcting RS code over  $\mathbb{F}_8$  of Example 1.1. Recall that the encoder takes a word of  $(\mathbb{F}_8)^3$  and ensures a codeword of  $(\mathbb{F}_8)^7$ , adding 4 parity-check symbols of  $\mathbb{F}_8$ .

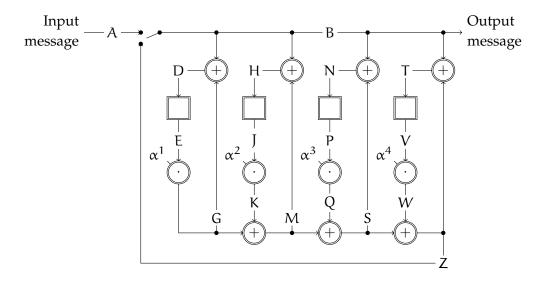

Figure 4.1: The encoder of Figure 1.5 with t=2. Each wire is labelled with a polynomial indeterminate.

The actual circuit is shown in Figure 4.1. The seventeen wires are each labelled with a letter from

$$\mathcal{L} := \{A, B, D, E, G, H, J, K, M, N, P, Q, S, T, V, W, Z\}.$$

The circuit requires seven clock cycles, so there is a total of 119 polynomial variables

$$\mathcal{L}^* := \{\ell_i \mid \ell \in \mathcal{L}, \ i = 1, \dots, 7\},\$$

that is to say, our environment ring will be  $\mathbb{F}_8[\mathcal{L}^*]$ .

We have now to translate the design of the circuit into an ideal. Table 4.1 lists the polynomials which arise from the various gates, as well as the field equations.

After that we define the specification polynomials. This encoding method is systematic, so the first three outputs have to be equal to the inputs:

$$f_1 := B_1 - A_1$$

$f_2 := B_2 - A_2$

$f_3 := B_3 - A_3$ .

Recall that, for a message  $\mathfrak{m}(X)$ , the parity-check symbols are obtained by dividing  $\mathfrak{m}(X) \cdot X^{2t}$  by g(X) and taking the coefficients of the remainder, where t is the error-correcting capability of the code and g is the generator polynomial. In

| Type of gate             | Polynomials                                                                                                         | Ranges                                 | #   |

|--------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|

| First row of adders      | $B_{i} + G_{i} - D_{i},  B_{i} + M_{i} - H_{i},  B_{i} + S_{i} - N_{i},  B_{i} + Z_{i} - T_{i}$                     | i = 1,, 7                              | 28  |

| Registers initialization | $E_1, J_1, P_1, V_1$                                                                                                |                                        | 4   |

| Registers                | $\begin{split} E_{i+1} - D_i, & J_{i+1} - H_i, \\ P_{i+1} - N_i, & V_{i+1} - T_i \end{split}$                       | $i=1,\ldots,6$                         | 24  |

| Multipliers              | $\begin{aligned} G_i - \alpha E_i, & K_i - \alpha^2 H_i, \\ Q_i - \alpha^3 P_i, & W_i - \alpha^4 V_i \end{aligned}$ | $i=1,\ldots,7$                         | 28  |

| Second row of adders     | $G_i + K_i - M_i,  M_i + Q_i - S_i,$<br>$S_i + W_i - Z_i$                                                           | $i=1,\ldots,7$                         | 21  |

| Switch                   | $B_{i} - A_{i}$ $B_{i} - Z_{i}$                                                                                     | $i = 1, \dots, 3$<br>$i = 4, \dots, 7$ | 7   |

| Field equations          | $\ell_{\mathfrak{i}}{}^{8}-\ell_{\mathfrak{i}}$                                                                     | $\ell_{i} \in \mathcal{L}^{*}$         | 119 |

|                          | Total number of polynomials                                                                                         |                                        | 231 |

Table 4.1: List of the polynomials associated to the circuit in Figure 4.1.

our case (t = 2, m(X) =

$$(A_1)X^2 + (A_2)X + (A_3)$$

)

$$m(X) \cdot X^{2t} = (A_1)X^6 + (A_2)X^5 + (A_3)X^4,$$

$$q(X) = X^4 + (\alpha + 1)X^3 + X^2 + \alpha X + (\alpha + 1),$$

and a quick computation gives us

$$\begin{split} f_4 &:= B_4 - \left( (\alpha^2 + \alpha) A_1 + \alpha^2 A_2 + (\alpha + 1) A_3 \right) \\ f_5 &:= B_5 - \left( A_1 + A_2 + A_3 \right) \\ f_6 &:= B_6 - \left( (\alpha^2 + \alpha) A_1 + (\alpha^2 + 1) A_2 + \alpha A_3 \right) \\ f_7 &:= B_7 - \left( (\alpha^2 + \alpha + 1) A_1 + (\alpha^2 + 1) A_2 + (\alpha + 1) A_3 \right). \end{split}$$

Let  $I \subseteq \mathbb{F}_8[\mathcal{L}^*]$  the ideal generated by the 231 polynomials of Table 4.1. Correctness of the circuit is established if  $f_i \in I$  for i = 1, ..., 7.

We tested our method with the Sage software on a Intel<sup>®</sup> Atom<sup>TM</sup> N550 processor @1.50 GHz with 2 GB RAM @667 MHz. First of all we have to set up the environment.

```

K. <a>=FiniteField(8);

```

```

R=PolynomialRing(K, "A1, A2, A3, A4, A5, A6, A7, B1, B2, B3, B4, B5, B6, B7, D1, D2, D3, D4, D5, D6, D7, E1, E2, E3, E4, E5, E6, E7, G1, G2, G3, G4, G5, G6, G7, H1, H2, H3, H4, H5, H6, H7, J1, J2, J3, J4, J5, J6, J7, K1, K2, K3, K4, K5, K6, K7, M1, M2, M3, M4, M5, M6, M7, N1, N2, N3, N4, N5, N6, N7, P1, P2, P3, P4, P5, P6, P7, Q1, Q2, Q3, Q4, Q5, Q6, Q7, S1, S2, S3, S4, S5, S6, S7, T1, T2, T3, T4, T5, T6, T7, V1, V2, V3, V4, V5, V6, V7, W1, W2, W3, W4, W5, W6, W7, Z1, Z2, Z3, Z4, Z5, Z6, Z7");

```

R.inject\_variables();

#### The next step is putting together all the equations into an ideal I:

```

I=Ideal (B1+G1-D1, B2+G2-D2, B3+G3-D3, B4+G4-D4, B5+G5-D5,

B6+G6-D6,B7+G7-D7,B1+M1-H1,B2+M2-H2,B3+M3-H3,B4+M4-H4,

B5+M5-H5, B6+M6-H6, B7+M7-H7, B1+S1-N1, B2+S2-N2, B3+S3-N3,

B4+S4-N4, B5+S5-N5, B6+S6-N6, B7+S7-N7, B1+Z1-T1, B2+Z2-T2,

B3+Z3-T3, B4+Z4-T4, B5+Z5-T5, B6+Z6-T6, B7+Z7-T7, E1, J1, P1,

V1, E2-D1, E3-D2, E4-D3, E5-D4, E6-D5, E7-D6, J2-H1, J3-H2,

J4-H3, J5-H4, J6-H5, J7-H6, P2-N1, P3-N2, P4-N3, P5-N4, P6-N5,

P7-N6, V2-T1, V3-T2, V4-T3, V5-T4, V6-T5, V7-T6, G1-a*E1,

G2-a*E2, G3-a*E3, G4-a*E4, G5-a*E5, G6-a*E6, G7-a*E7,

K1-(a^2)*J1, K2-(a^2)*J2, K3-(a^2)*J3, K4-(a^2)*J4,

K5-(a^2)*J5, K6-(a^2)*J6, K7-(a^2)*J7, Q1-(a^3)*P1,

Q2-(a^3)*P2,Q3-(a^3)*P3,Q4-(a^3)*P4,Q5-(a^3)*P5,

Q6-(a^3)*P6,Q7-(a^3)*P7,W1-(a^4)*V1,W2-(a^4)*V2,

W3-(a^4)*V3, W4-(a^4)*V4, W5-(a^4)*V5, W6-(a^4)*V6,

W7-(a^4) * V7, G1+K1-M1, G2+K2-M2, G3+K3-M3, G4+K4-M4,

G5+K5-M5, G6+K6-M6, G7+K7-M7, M1+Q1-S1, M2+Q2-S2, M3+Q3-S3,

M4+Q4-S4, M5+Q5-S5, M6+Q6-S6, M7+Q7-S7, S1+W1-Z1, S2+W2-Z2,

S3+W3-Z3,S4+W4-Z4,S5+W5-Z5,S6+W6-Z6,S7+W7-Z7,B1-A1,

B2-A2, B3-A3, B4-Z4, B5-Z5, B6-Z6, B7-Z7, A1^8-A1, A2^8-A2,

A3^8-A3, A4^8-A4, A5^8-A5, A6^8-A6, A7^8-A7, B1^8-B1, B2^8-B2,

B3^8-B3, B4^8-B4, B5^8-B5, B6^8-B6, B7^8-B7, D1^8-D1, D2^8-D2,

D3^8-D3, D4^8-D4, D5^8-D5, D6^8-D6, D7^8-D7, E1^8-E1, E2^8-E2,

E3^8-E3, E4^8-E4, E5^8-E5, E6^8-E6, E7^8-E7, G1^8-G1, G2^8-G2,

G3^8-G3,G4^8-G4,G5^8-G5,G6^8-G6,G7^8-G7,H1^8-H1,H2^8-H2,

H3^8-H3, H4^8-H4, H5^8-H5, H6^8-H6, H7^8-H7, J1^8-J1, J2^8-J2,

J3^8-J3, J4^8-J4, J5^8-J5, J6^8-J6, J7^8-J7, K1^8-K1, K2^8-K2,

K3^8-K3, K4^8-K4, K5^8-K5, K6^8-K6, K7^8-K7, M1^8-M1, M2^8-M2,

M3^8-M3, M4^8-M4, M5^8-M5, M6^8-M6, M7^8-M7, N1^8-N1, N2^8-N2,

```

```

N3^8-N3,N4^8-N4,N5^8-N5,N6^8-N6,N7^8-N7,P1^8-P1,P2^8-P2,P3^8-P3,P4^8-P4,P5^8-P5,P6^8-P6,P7^8-P7,Q1^8-Q1,Q2^8-Q2,Q3^8-Q3,Q4^8-Q4,Q5^8-Q5,Q6^8-Q6,Q7^8-Q7,S1^8-S1,S2^8-S2,S3^8-S3,S4^8-S4,S5^8-S5,S6^8-S6,S7^8-S7,T1^8-T1,T2^8-T2,T3^8-T3,T4^8-T4,T5^8-T5,T6^8-T6,T7^8-T7,V1^8-V1,V2^8-V2,V3^8-V3,V4^8-V4,V5^8-V5,V6^8-V6,V7^8-V7,W1^8-W1,W2^8-W2,W3^8-W3,W4^8-W4,W5^8-W5,W6^8-W6,W7^8-W7,Z1^8-Z1,Z2^8-Z2,Z3^8-Z3,Z4^8-Z4,Z5^8-Z5,Z6^8-Z6,Z7^8-Z7);

```

```

G=I.groebner_basis();

```

The Gröbner basis<sup>[1]</sup> of I has 119 polynomials and has been computed in 1.86 s. Now we define the specification polynomials.

```

f1=B1-A1;

f2=B2-A2;

f3=B3-A3;

f4=B4-(a^2+a)*A1-(a^2)*A2-(a+1)*A3;

f5=B5-A1-A2-A3;

f6=B6-(a^2+a)*A1-(a^2+1)*A2-(a)*A3;

f7=B7-(a^2+a+1)*A1-(a^2+1)*A2-(a+1)*A3;

```

The correctness of the circuit is established once we have verified that

$$f_1, \ldots, f_7 \in I$$

for which we can ask Sage:

```

[f1.reduce(G), f2.reduce(G), f3.reduce(G), f4.reduce(G),

f5.reduce(G), f6.reduce(G), f7.reduce(G)];

```

The answer is

```

[0, 0, 0, 0, 0, 0, 0]

```

and we can conclude that the circuit works correctly.

### 4.1.2 2-Error-Correcting RS over $\mathbb{F}_8$ with a Bug

Now suppose that there is a bug in the circuit implementation. In this example, we change one of the adders of the second row with a multiplier (see Figure 4.2). The only difference in I is that the polynomials  $M_i + Q_i - S_i$  become  $M_iQ_i - S_i$ .

We tried to perform the computation, but after more than 6 hours both the 2 GB RAM and the 1 GB SWAP memories got saturated, and we didn't manage to obtain a Gröbner basis.

$<sup>\</sup>ensuremath{^{[1]}}\ensuremath{\text{Sage}}$  uses the degrevlex monomial ordering by default.

Figure 4.2: A bug in the circuit of Figure 4.1.

### **4.1.3 4-Error-Correcting RS over** $\mathbb{F}_{32}$

For the last example we choose the field  $\mathbb{F}_{32}$ , implemented as  $\mathbb{F}_2[\alpha]$  with minimal polynomial  $\alpha^5 + \alpha^2 + 1$ , and t = 4, so that we have 23 message symbols and 8 check symbols. The generator polynomial is

$$g(X) := (X - \alpha) \cdot \ldots \cdot (X - \alpha^8).$$

There are 33 wires and 31 clock cycles are needed, for a total of 1023 polynomial indeterminates. In particular, we will work in  $\mathbb{F}_{32}[\mathcal{L}^*]$  with

$$\mathcal{L} := \{A, B, C, D, E, F, G, H, I, J, K, L, M, N, O, P, Q, R, S, T, U, V, W, X, Y, Z, \Gamma, \Theta, \Lambda, \Xi, \Phi, \Psi, \Omega\}$$

and  $\mathcal{L}^* := \{\ell_i \mid \ell \in \mathcal{L}, \ i = 1, \dots, 31\}$ . It is not difficult to write the polynomial constraint of this circuit: they are similar to the ones seen before. We will not report them here, mainly because they take too much space—there are 992 polynomials which arise from the gates and 1023 field equations, which means a total of 2015 polynomials!

The first 23 specification polynomials are  $f_i := B_i - A_i$  (for i = 1, ..., 23), because the encoding is systematic. These already belong to the ideal defined by the circuit (they appear in the description of the switch), so we may ignore them. A (not so) quick computation gives the formulas for the other outputs.

$$\begin{split} f_{24} &:= B_{24} + (\alpha^4 + \alpha^2 + \alpha + 1)A_1 + (\alpha^3 + \alpha^2)A_2 + (\alpha^3 + \alpha^2 + \alpha + 1)A_3 + \\ &\quad + (\alpha^4 + \alpha^3)A_4 + (\alpha^4 + \alpha^2 + 1)A_5 + (\alpha^4)A_6 + (\alpha^4 + \alpha^3 + \alpha^2 + 1)A_7 + \\ &\quad + (\alpha^4 + \alpha^2 + \alpha)A_8 + (\alpha^4 + \alpha^3 + \alpha^2 + \alpha)A_9 + (\alpha^4 + \alpha^3 + \alpha)A_{10} + \\ &\quad + (\alpha^3 + \alpha + 1)A_{11} + (\alpha)A_{12} + (\alpha^3 + \alpha^2 + \alpha)A_{13} + (\alpha^3 + 1)A_{14} + \\ &\quad + (\alpha^2)A_{15} + (\alpha^3 + \alpha^2 + 1)A_{16} + (\alpha^3)A_{17} + (\alpha^2 + \alpha + 1)A_{18} + \\ &\quad + (\alpha^3 + \alpha^2 + \alpha + 1)A_{19} + (\alpha)A_{20} + (\alpha^4 + \alpha^2 + 1)A_{21} + \end{split}$$

Figure 4.3: The encoder with t=4.

$$\begin{split} &+(\alpha^4+\alpha^3+\alpha^2+\alpha+1)A_{22}+(\alpha^3)A_{23} \\ &f_{25} \coloneqq B_{25}+(\alpha^3+1)\lambda_1+(\alpha^4+\alpha^3)\lambda_2+(\alpha^4+\alpha^3+\alpha+1)\lambda_3+(\alpha^4+1)\lambda_4+\\ &+A_5+A_6+(\alpha+1)A_7+(\alpha^4+\alpha^3+\alpha^2)A_8+(\alpha^4+\alpha^3+\alpha^2+1)A_9+\\ &+(\alpha^4)A_{10}+(\alpha^3)A_{11}+(\alpha^4+\alpha^3+\alpha^2)A_{14}+(\alpha^3+\alpha^2)A_{15}+\\ &+(\alpha^4+\alpha^3+\alpha^2+1)A_{13}+(\alpha^3+\alpha^2)A_{14}+(\alpha^3+\alpha^2)A_{15}+\\ &+(\alpha+1)A_{16}+(\alpha^2+\alpha+1)A_{17}+(\alpha^4+\alpha^2+1)A_{18}+(\alpha^4)A_{19}+\\ &+(\alpha^4+\alpha^3+\alpha^2+\alpha+1)A_{20}+(\alpha^4+\alpha^3+\alpha+1)A_{21}+\\ &+(\alpha^4+\alpha^3+\alpha^2+\alpha+1)A_{21}+(\alpha^4+\alpha^2+1)A_{33}+\\ &+(\alpha^4+\alpha^2+\alpha)A_{22}+(\alpha^4+\alpha^2+1)A_{23}+\\ &f_{26} \coloneqq B_{26}+(\alpha^4+\alpha+1)A_1+(\alpha^3+\alpha^2+\alpha)A_2+(\alpha^2+1)A_3+\\ &+(\alpha^4+\alpha^2+1)A_4+(\alpha^3+\alpha^2+1)A_5+(\alpha^4+\alpha^2+\alpha)A_6+(\alpha^2)A_7+\\ &+(\alpha^2+1)A_8+(\alpha+1)A_9+(\alpha^4+\alpha^3+\alpha^2)A_{10}+(\alpha^4+\alpha+1)A_{11}+\\ &+(\alpha^2+\alpha+1)A_{12}+(\alpha^4+\alpha+1)A_{13}+(\alpha^4+1)A_{14}+(\alpha^4+\alpha)A_{15}+\\ &+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_{16}+(\alpha^4+\alpha^3+\alpha)A_{17}+(\alpha+1)A_{18}+\\ &+(\alpha^3)A_{19}+(\alpha^4+\alpha^3+\alpha^2+\alpha+1)A_{20}+(\alpha+1)A_{21}+(\alpha^4+1)A_{22}+\\ &+(\alpha^3+\alpha^2+\alpha+1)A_1+(\alpha^3+\alpha^2+\alpha)A_6+(\alpha^4+\alpha^3+\alpha)A_{17}+(\alpha+1)A_{18}+\\ &+(\alpha^3+\alpha^3+\alpha^2+\alpha)A_{16}+(\alpha^4+\alpha^3+\alpha)A_{17}+(\alpha+1)A_{18}+\\ &+(\alpha^4+\alpha^3+1)A_4+(\alpha^3)A_5+(\alpha^2+\alpha)A_6+(\alpha^4+\alpha^3+\alpha)A_{11}+\\ &+(\alpha^4+\alpha^3+1)A_1+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_9+A_{10}+(\alpha^4+\alpha^3+\alpha)A_{11}+\\ &+(\alpha^3+\alpha^2+1)A_{12}+(\alpha^4+\alpha^2+\alpha)A_{20}+(\alpha)A_{21}+\\ &+(\alpha^4+\alpha^3+\alpha^2)A_{19}+(\alpha^4+\alpha^2+\alpha)A_{20}+(\alpha)A_{21}+\\ &+(\alpha^4+\alpha^3+\alpha^2)A_{19}+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_{11}+\\ &+(\alpha^4+\alpha^3+\alpha^2)A_{19}+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_{21}+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_{11}+\\ &+(\alpha^4+\alpha^2+\alpha)A_{12}+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_{11}+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_{11}+\\ &+(\alpha^4+\alpha^2+\alpha)A_{12}+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_{11}+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_{11}+\\ &+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_{11}+(\alpha^4+\alpha^3+\alpha^3+\alpha^2+\alpha)A_{11}+\\ &+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_{11}+(\alpha^4+\alpha^3+\alpha^3+\alpha)A_{11}+(\alpha^4+\alpha^3+\alpha^2+\alpha)A_{13}+\\ &+(\alpha^4+\alpha^3+\alpha^2$$

4.2. General Case 35

$$+ (\alpha^4 + \alpha^3 + \alpha^2 + \alpha)A_{14} + (\alpha^3 + \alpha^2)A_{15} + (\alpha^3 + 1)A_{16} + \\ + (\alpha^4 + \alpha + 1)A_{17} + (\alpha^3)A_{18} + (\alpha^2 + 1)A_{19} + (\alpha^4 + 1)A_{20} + \\ + (\alpha^4 + \alpha^3 + \alpha^2 + \alpha + 1)A_{21} + (\alpha^4 + \alpha^3 + \alpha^2)A_{22} + (\alpha^4 + \alpha^3 + \alpha)A_{23}$$

$$f_{30} := B_{30} + (\alpha^4)A_1 + (\alpha)A_2 + (\alpha^2 + \alpha + 1)A_3 + (\alpha)A_4 + (\alpha^3 + \alpha^2 + \alpha)A_5 + \\ + (\alpha^4 + \alpha^3)A_6 + (\alpha)A_7 + (\alpha^4 + \alpha)A_8 + (\alpha^3 + \alpha^2 + \alpha + 1)A_9 + \\ + (\alpha^4 + \alpha^3 + \alpha^2 + 1)A_{10} + (\alpha^4 + \alpha)A_{11} + (\alpha^3 + \alpha^2 + \alpha + 1)A_{12} + \\ + (\alpha)A_{13} + (\alpha^4 + \alpha^3 + \alpha^2 + \alpha)A_{14} + (\alpha^4 + \alpha^3 + 1)A_{15} + \\ + (\alpha^4 + \alpha^3 + \alpha^2 + \alpha + 1)A_{16} + (\alpha^2 + \alpha + 1)A_{17} + \\ + (\alpha^4 + \alpha^3 + \alpha^2 + \alpha + 1)A_{18} + (\alpha^3 + \alpha)A_{19} + (\alpha^4 + \alpha^2)A_{20} + \\ + (\alpha^4)A_{21} + A_{22} + (\alpha^4 + \alpha)A_{23}$$

$$f_{31} := B_{31} + (\alpha^4 + \alpha^3 + 1)A_1 + (\alpha^4 + \alpha^2 + \alpha)A_2 + (\alpha^4 + \alpha^2 + \alpha + 1)A_3 + \\ + (\alpha^3 + \alpha + 1)A_4 + (\alpha^4 + \alpha^3 + \alpha)A_5 + (\alpha^2 + \alpha)A_6 + (\alpha^2)A_7 + \\ + (\alpha^3 + 1)A_8 + (\alpha^4 + \alpha^3 + \alpha^2 + 1)A_9 + (\alpha)A_{10} + (\alpha^3 + \alpha)A_{11} + \\ + (\alpha^4 + \alpha + 1)A_{12} + (\alpha^3)A_{13} + (\alpha^4 + \alpha^2)A_{14} + (\alpha^4 + \alpha^3 + \alpha^2)A_{15} + \\ + (\alpha^3 + \alpha^2 + 1)A_{16} + (\alpha^4 + \alpha^3 + \alpha + 1)A_{17} + (\alpha^4 + \alpha^2 + \alpha)A_{18} + \\ + (\alpha^3 + \alpha)A_{19} + (\alpha^3 + \alpha + 1)A_{20} + (\alpha^3 + \alpha^2)A_{21} + \\ + (\alpha^3 + \alpha^2 + 1)A_{22} + (\alpha^2 + 1)A_{23}$$

Having in mind the failure in computing the Gröbner basis of the previous example, we tried to bypass the problem. Remember that the circuit is linear, and the biggest part of the computation is the reduction of the field equations. Fortunately, we may apply the results of Section 2.5, so only the 992 polynomials from the circuit are needed. Our PC took 30.1s to compute the 992 polynomials of the Gröbner basis  $\Im$  of this smaller ideal. All the  $f_i$ 's reduce to zero with respect to  $\Im$ , from which we may conclude that this instance of the circuit works.

#### 4.2 General Case

In this section we describe the circuit with a system of difference equations and try to deduce the correctness from these. Actually, there are *two* sets of equations that control the behaviour of the circuit: before turning the switch and after.

Notational Remark. In order to not carry the 2 in the formulas, in this section we will suppose that there are t check symbols (instead of 2t). Moreover, we suppose that the switch is activated after k symbols, so that the time indexes from 0 to k-1 refer to the circuit before turning down the switch. The total number of cycles required is n = k + t (time indexes from 0 to n - 1).

Figure 4.4: The same of Figure 1.5.

Figure 4.4 is the same of Figure 1.5, which we recall here for convenience. Let  $\mathfrak{u}(s)$  ( $s \in \mathbb{N} \setminus \{0\}$ ) be the sequence of the inputs,  $\mathfrak{y}(s)$  the one of the outputs, and  $\mathfrak{x}(s) = (x_1(s), \ldots, x_t(s))$  the content of the t registers, which will represent the state of the circuit.

Let us begin from the first phase of the circuit, i.e. when the switch is in the upper position. The equation for the output is easy:

$$y(s) = u(s)$$

because the encoding is systematic. Let us focus on the state; the i-th register at time s+1 receives the result of the adder in the first row, which adds the input and the result of

$$\alpha x_1(s) + \alpha^2 x_2(s) + \dots + \alpha^i x_i(s). \tag{4.1}$$